Notes on RISC-V CPU HARD IP Cores enter SoC FPGAs

- Related pages

Notes on RISC-V CPU HARD IP Cores enter SoC FPGAs presentation

- Frozen base ISA

- Consolidation in the semiconductor industry

- RISC-V is not owned by anyone

- Custom instruction extension to extend the virtuous cycle of semiconductor innovation

PolarFire SoC - RISC-V enabled innocation platform #

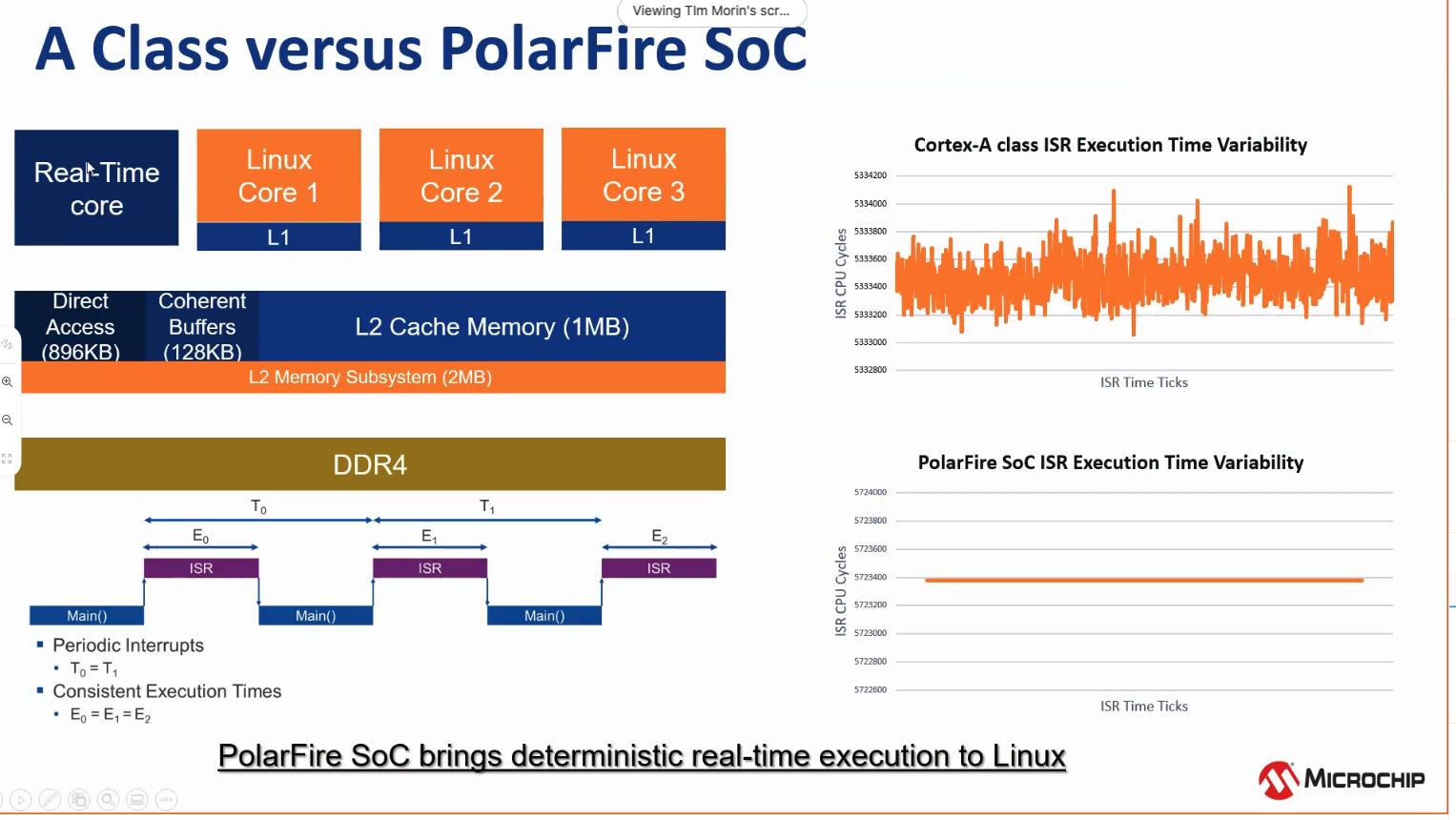

- Mixed critically RTOS + Linux support

- Defence grade security

- Exceptional reliability

- Designed for low-power

- L2 memory subsystem

- Can be made to be deterministic

- Not all L2 are deterministic